# UNIVERSITY OF GAZÍANTEP

Electrical and Electronic Eng. Dept.

EEE 441 LOGICAL DESIGN II

LABORATORY EXPERIMENT 3

SEQUENTIAL CIRCUIT DESIGN-I

#### 1 OBJECT

In this experiment you will design, construct and test three synchronous sequential circuit. Use J-K flip-flops(IC 7476) in your designs.

#### 2 PRELIMINARY WORK

(P1) Design a 2-bit counter that counts up or down. An enable input E determines whether the counter is on or off. If E=0, the counter is disable and remains at its present count even though clock pulses are applied. If E=1, the counter is enabled and a second input, x, determines the count direction. If x=1, the circuit counts up with the sequence 00, 01, 10, 11 and repeats. If x=0, the circuit counts down with the sequence 11, 10, 01, 00 and repeats. Design the sequential circuits with E and x inputs.

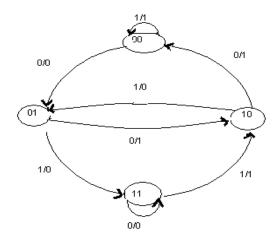

**(P2)** Design a sequential circuit whose state diagram is shown below. Designate the two flip-flops as A and B, the input as x, and the output as y.

(P3) Design a counter that goes through the following sequence of binary states: 0, 1, 2, 3, 6, 7, 10, 11, 12, 13, 14, 15 and back to 0 to repeat. Note that binary states 4, 5, 8 and 9 are not used. The counter must be self-starting; that is if the circuit starts from any one of the four invalid states, the count pulses must transfer the circuit to one of the valid states to continue the count correctly.

### 3 EXPERIMENTAL PROCEDURE

- (E1) Construct the circuit you designed in P1 and verify its operation.

- (E2) Construct the circuit you designed in P2 and verify the state transition and output by testing the circuit.

- (E3) Construct the circuit you designed in P3 and check the circuit operation for the required count sequence. Verify that the counter is self-starting. This can be done by initializing the circuit to each unused state by means of the PRE and CLR inputs and then applying pulses to see if the counter reaches to one of the valid states.

## 4 EQUIPMENT LIST

7400 quad 2-input NAND gate 7404 hex inverter 7476 dual JK master-slave flip-flop